![[디지털 공학(26)] Memory(메모리)](https://img1.daumcdn.net/thumb/R750x0/?scode=mtistory2&fname=https%3A%2F%2Fblog.kakaocdn.net%2Fdn%2FuhQhV%2FbtsHbntQfG7%2FU0xs20NkbzAOoABmmNVSYK%2Fimg.png)

안녕하세요.

디지털 공학 카테고리의 마지막으로 메모리 회로 설계에 대해 알아보고 직접 설계해볼수 있도록 준비하였습니다. 마지막 메모리 설계에 대한 답은 가렸습니다. 직접 진행해보시고 해답이나 솔루션 필요시 답글주세요.

회로설계에 대한 부분은 블러 처리 할테니 직접 진행해보세요.

질문이나 솔루션 필요시 답글에 달아주세요!!

※1. bit, byte의 개념

※2. Memory Addressing

※3. Memory의 종류

(1) RAM : 휘발성(전원이 켜져 있을 때만 저장가능)

Read, Write가 가능

(2) ROM : 비휘발성(전원이 꺼져있어도 저장가능)

Read만 가능

※4. Memory Controller 설계

문제| 아래의 Memory controller 회로를 설계하고 그 내용을 설명하시오.

Solution)

▶1. Address Generator Symbol 제작

⓵ Address Generator (4진 2bit카운터 제작) 회로

=> 여기표(Excitation table)를 사용하지 않고 직관적인 방법으로 간단하게 설계가 가능하다.

+ ) => 비동기 카운터

=> FF 2개 사용 => 4진 카운터

=> Clock에 버블 붙지 않음 => Raising edge에서 동작

=> Q‘의 출력을 입력 받음 => Up카운터

⓶Address Generator의 타이밍도

=> 0~3을 반복하는 카운터를 제작 하였다.(RST이 0일 때 Reset)

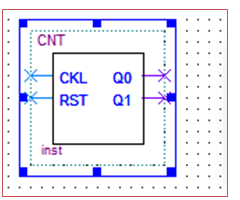

⓷ Address Generator Symbol

=> CNT로 심볼화 하였다.

▶2. Address Decoder Symbol 제작

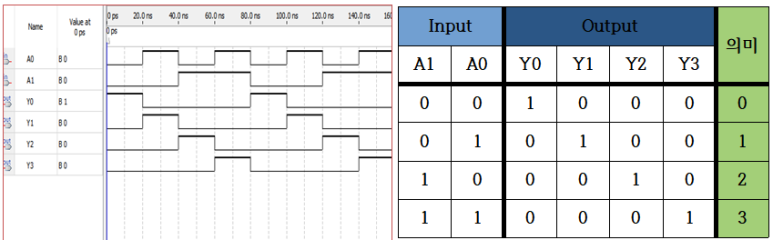

⓵ Address Decoder 회로

=> 2비트 신호를 각각의 경우에 맞추어 입력이 00일 때

Y0=1 / 01일 때 Y1=1 / 10일 때 Y2=1 / 11일 때 Y3=1을 출력한다.

⓶ Address Decoder의 타이밍도

=> 2개의 입력으로 들어오는 데이터를 받아 4개의 출력 회선 중 그 숫자에 해당하는 곳에 출력을 내보내는 회로

ex) Y1에 출력에 1이 출력되면 1를 의미

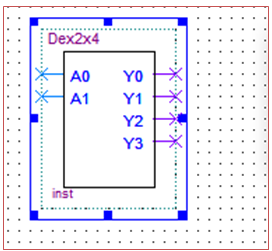

⓷Address Decoder Symbol

=> Dex2x4로 심볼화 하였다.

▶3. Byte organized Memory array Symbol 제작

⓵ Byte organized Memory array 회로

AA를 2진수로 나타내면 1010 1010 이고 가장 왼쪽 F/F이 MSB 이므로 0101 0101을 각각의 F/F에 입력

BB를 2진수로 나타내면 1011 1011 이고 가장 왼쪽 F/F이 MSB 이므로 1101 1101을 각각의 F/F에 입력

CC를 2진수로 나타내면 1100 1100 이고 가장 왼쪽 F/F이 MSB 이므로 0011 0011을 각각의 F/F에 입력

DD를 2진수로 나타내면 1101 1101 이고 가장 왼쪽 F/F이 MSB 이므로 1011 1011을 각각의 F/F에 입력

⓶ Byte organized Memory array의 타이밍도

=> CK가 Raising Edge일 때 다음 신호로 바뀌어 지는 것을 볼수 있다.

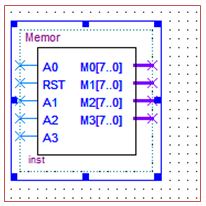

⓷ Byte organized Memory array Symbol

=> 심볼 화 하였다.(RST를 가장 하단으로 뻇으면 더 편리했을 것이다....)

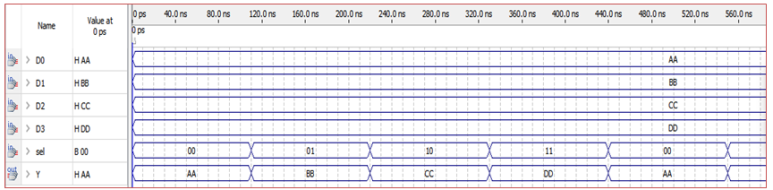

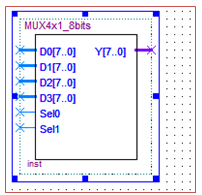

▶4. MUX 4*1_8bit Symbol 제작

⓵ MUX 4x1_8Bit 회로

- 지정된 시간 순서로 여러 입력 라인의 디지털 데이터를 단일 출력 라인으로 전환하는 논리회로

- 데이터 입력선의 선택은 선택 입력(SEL)에 의해 결정됨.

- n개의 선택 입력(SEL)의 경우 2^n개까지 입력 신호에 관한 회로 구성이 가능하다.

=> Sel이 00=>AA 01=>BB 10=>CC 11=>DD를 출력하는 기능을 가진 Multiplexer를 설계하였다.

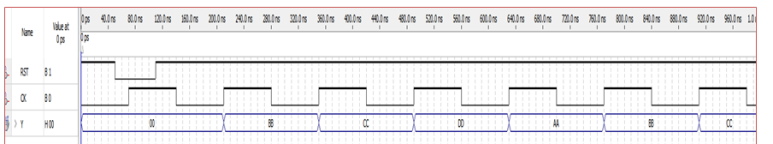

⓶ MUX 4x1_8Bit 타이밍도

=> Sel이 00=>AA 01=>BB 10=>CC 11=>DD을 출력하는 결과나 나왔다.

⓷ MUX 4*1 8Bit Symbol

=>MUX4*1 8Bits로 심볼화 하였다.

|Result!!|

⓵ Memory controller 회로

(=>Memor의 RST입력단자를 아래로 뺏으면 좀 더 깔끔한 회로가 구성되었을 것이다.)

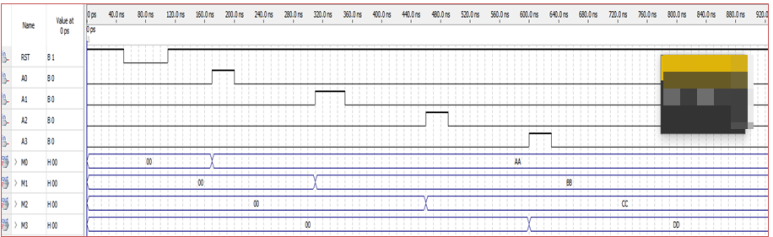

⓶ Memory controller 타이밍도

⓷ Result!!

=> 최종적으로 처음으로 변환되는 00의 신호를 제외하고는 Clock신호가 Rasing Edge 일 때BB-CC-DD-AA-BB-CC-DD-AA....가 반복되는 회로를 구상할 수 있었다. (원래 AA가 나와야하는 처음의 변동 신호에는 불안정으로 다른 값이 나온 것임)

'University curriculum > [Course] Digital Engineering' 카테고리의 다른 글

| [디지털 공학(25)] Shift Register(시프트 레지스터)_순서논리회로 (7) (0) | 2024.05.12 |

|---|---|

| [디지털 공학(24)] Up/Down Counter(업 다운 카운터)_순서논리회로(6) (0) | 2024.05.12 |

| [디지털 공학(23)] State Machine(상태기계)_순서논리회로(5) (1) | 2024.05.11 |

| [디지털 공학(22)] 불규칙 카운터_순서논리회로(4) (0) | 2024.05.11 |

| [디지털 공학(21)] Synchronism Counter(동기 카운터)_순서논리회로(3) (0) | 2024.05.11 |

전자공학 블로그에 오신 것을 환영합니다! 최신 기술 동향, 회로 설계, 반도체 및 전자 부품에 대한 유용한 정보와 실습 팁을 제공합니다.

![[디지털 공학(25)] Shift Register(시프트 레지스터)_순서논리회로 (7)](https://img1.daumcdn.net/thumb/R750x0/?scode=mtistory2&fname=https%3A%2F%2Fblog.kakaocdn.net%2Fdn%2Fc0TJQ6%2FbtsHcS0xNAI%2FfFipCk2IwXOu7DJJD0x7a1%2Fimg.png)

![[디지털 공학(24)] Up/Down Counter(업 다운 카운터)_순서논리회로(6)](https://img1.daumcdn.net/thumb/R750x0/?scode=mtistory2&fname=https%3A%2F%2Fblog.kakaocdn.net%2Fdn%2FbTB6t4%2FbtsHcaAwXEe%2FggQDsGn9kkFmK91YImsmgk%2Fimg.png)

![[디지털 공학(23)] State Machine(상태기계)_순서논리회로(5)](https://img1.daumcdn.net/thumb/R750x0/?scode=mtistory2&fname=https%3A%2F%2Fblog.kakaocdn.net%2Fdn%2FcGKbEf%2FbtsHe1biPwH%2Fk67jKYuKU2Szp6K0OG4sw0%2Fimg.png)

![[디지털 공학(22)] 불규칙 카운터_순서논리회로(4)](https://img1.daumcdn.net/thumb/R750x0/?scode=mtistory2&fname=https%3A%2F%2Fblog.kakaocdn.net%2Fdn%2Fd6Xtyi%2FbtsHcTyixV4%2FaKeUvEMgVz3xVC9nk2vkF0%2Fimg.png)