![풀 업 / 풀 다운 [Pull Up / Pull Down ] 저항 ( 플로팅 원리, 회로 구성 )](https://img1.daumcdn.net/thumb/R750x0/?scode=mtistory2&fname=https%3A%2F%2Fblog.kakaocdn.net%2Fdn%2FdBGtAD%2FbtsHKE9rBfA%2FcVbnHhrXABPkM47Ui3kVkk%2Fimg.png)

안녕하세요.

풀업 저항(pull-up resistor)과 풀다운 저항(pull-down resistor)은 디지털 회로에서 중요한 역할을 하는 구성 요소입니다. 이 저항들은 입력 핀이 안정적인 전압 상태를 유지하게 도와줍니다. 각 저항의 동작 원리와 용도에 대해 자세히 설명하겠습니다.

※1. 풀업 저항 / 풀다운 저항 (Pull-up / Pull-Down Resistor)

풀업 / 풀다운 저항의 필요성과 원리 및 회로 구성에 대해 알아보겠습니다.

▶1. Voltage Level과 플로팅 ( Floating) 현상

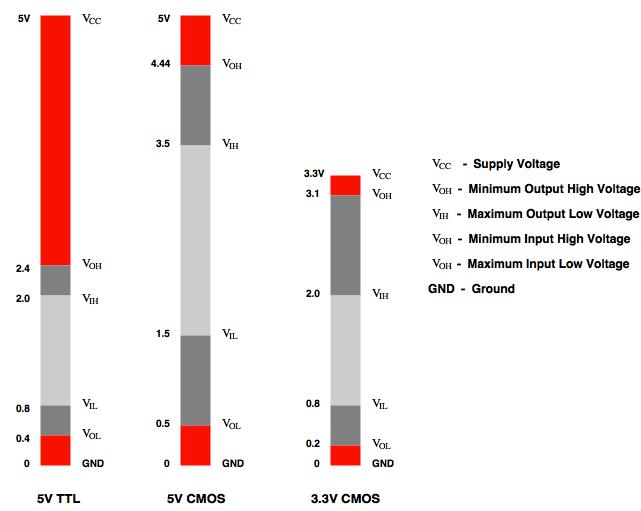

TTL(Transistor-Transistor Logic)과 CMOS(Complementary Metal-Oxide-Semiconductor)는 디지털 회로에서 사용되는 두 가지 주요 논리 게이트 기술입니다. ( 쉽게 설명해드리면 우리가 흔히 말하는 0(Low)와 1(High)를 구분할때 Voltage 크기를 사용하는데, 이때 Low와 High를 구분하기 위한 전압 범위 (Voltage Range)를 의미하고 이를 동작 전압 (Operating Voltage)이라고도 합니다.)

만약 아래의 이미지를 참조하여 TTL의 경우 High와 Low신호를 구분할 때 생기는 문제에 대해 설명해드리겠습니다. 5V TTL의 경우 0~0.8[V]의 전압이 들어올 경우 Low(0)으로 판별하고 2~5[V]의 전압은 High로 판별합니다. 그러면 사이의 전압 0.8~2.0[V]를 어떻게 판별되는가에 대한 문제가 발생합니다. 실제 디지털 논리 관점에서 해당 전압값이 입력되면 언제는 High, 언제는 Low가 불규칙적으로 나오게 되는 등 분명 비규칙적, 설계상 오류에 해당되고 회로의 동작에 있어서 큰 문제를 야기할 수 있습니다.

그러면 설계자가 0.8~2.0[V]를 통과하지 않게 하면되지 않는가? 생각 할 수 있겠지만 다음과 같은 이유 때문에 불가능하다고 생각하면됩니다.

1. 전기적 연결 없음

입력 핀이 VCC나 GND와 명확하게 연결되지 않은 경우, 핀은 외부 환경의 전자기적 간섭이나 내부 회로의 잡음에 영향을 받게 됩니다. 이로 인해 핀이 임의의 전압을 가지게 되고, 예측할 수 없는 동작을 하게 됩니다.

2. 잡음 및 간섭

입력 핀이 전기적으로 떠 있는 상태에서는 외부 전자기 간섭(EMI)이나 내부 회로의 잡음에 민감해집니다. 이러한 잡음은 핀의 전압을 불안정하게 만들며, 이를 통해 디지털 회로가 HIGH나 LOW 상태를 불규칙적으로 읽을 수 있습니다.

3. 입력 임피던스

디지털 입력 핀은 높은 임피던스를 가지며, 이는 작은 전류 변화에도 민감하게 반응하게 만듭니다. 핀이 떠 있는 상태에서는 주변 회로나 공기 중의 전자기파에 의해 전압이 변동될 수 있습니다.

이처럼 GND쪽으로 안착되거나 Vcc쪽으로 천장에 붙는 상태가 아닌 중간에 떠있는 상태를 "떠있다" 라는 의미에서 플로팅(Floating)상태이며 이로 인해 앞서 언급한 회로에서 논리 판별에 오류를 야기할때 플로팅 현상이 발생한다고 말합니다.

플로팅 상태의 입력 핀은 명확한 논리 상태(HIGH 또는 LOW)를 가지지 않기 때문에, 디지털 회로의 동작이 예측 불가능해집니다. 이는 다음과 같은 문제를 초래할 수 있습니다:

- 불안정한 신호: 입력 신호가 불규칙하게 변동하여, 원하는 동작을 수행하지 못하게 됩니다.

- 오작동: 디지털 회로가 잘못된 데이터를 처리하거나, 불필요한 동작을 수행할 수 있습니다.

- 전력 소비 증가: 불안정한 상태로 인해 회로의 전력 소비가 증가할 수 있습니다.

이 두 기술은 입력 핀의 플로팅 문제를 해결하는 데 도움이 되는 풀업 및 풀다운 저항과도 관련이 있습니다. 각각의 개념을 설명하고, 이를 바탕으로 풀업 및 풀다운 저항에 대해 다시 설명하겠습니다.

▶2. Pull Down 저항 / Pull Up 저항의 원리

스위치를 사용하는 회로에서 풀업 / 풀다운의 회로적 원리를 알아보겠습니다.

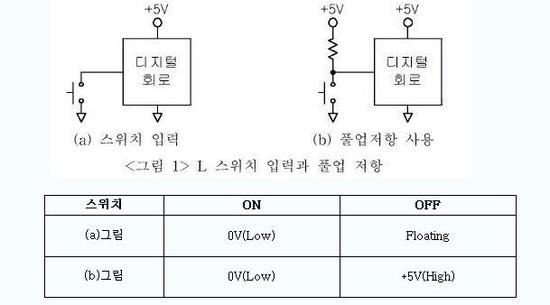

- 풀 다운 방식: 아래 (a)는 플로팅 현상이 발생하는 상태일 수 있습니다. (b)는 풀 다운 저항을 적용해 놓았기에(저항을 GND쪽에 연결) 플로팅 상태에서 Low Level을 가집니다.

:(a) 상태에서 이상적으로 Swith가 Off 상태이므로 전압이 인가되지 않고 있다고 볼수 있으나 이미 위에서 언급한 이유로 인해 일반적으로 0~1[V] 사이에 전압이 흐르고 있는 상태입니다. 그러므로 Floating Range안에 포함되서 회로의 논리적 판별의 오류를 갖게 될수 있습니다. 이때 (b)와 같이 Pull Down 저항을 연결하면 Switch가 Off 상태에서 0~1[V]의 전압을 가지는 미세 전류들이 저항이 연결된 GND쪽으로 빠지게됩니다.

Why?

-> 디테일 하게 들어가면 임력 임피던스, 라인 임피던스, 신호 특성을 복잡해져서 간단하게만 말씀드리면 Swith가 Off 상태일때 스위치가 연결되어 있는 5[V] 지점은 더 이상 의미가 없어지고 직렬로 "GND - 풀다운 저항 - 디지털 회로"로 이뤄진 회로가 됩니다. 이때 디지털 회로쪽에도 저항을 사용하지 않아도 분명 저항값이 적게라도 존재합니다. 전선으로 사용하는 (구리선도 저항이 0[ohm]이 아니라 작게 저항값을 가지고 있어요.) 그런데 직렬로 연결된 " 풀다운저항 - 전선 - 디지털회로저항" 회로에서 풀다운저항>>디지털회로저항 처럼 한쪽이 훨씬 큰 크기의 저항을 갖는다면 풀다운저항에 대부분의 전압이 먹히게 됩니다. 실제 저항의 전압 분배 원리에 따라 해당 경우 다음과 같은 전압을 분배 받습니다.저항1에서의 전압 값 = 5[V]X(저항1/(저항1+저항2))[V]

저항2에서의 전압 값 = 5[V]x(저항2/(저항1+저항2))[V]전류는 전압이 높은 곳에서 낮은 쪽으로 흐릅니다. 이말은 즉슨 직렬 회로에서 전류는 작은 저항을 갖는 쪽으로 흐릅니다. 즉 전류는 GND쪽으로 흐르고 디지털 회로쪽으로는 흐르지 않아 0[V]를 받는 것을 의미하여 신호의 관점에서 Low Level로 판별하는 것 입니다. 요약하자면 풀 다운 저항은 스위치가 Off 상태에서미세 전류의 방향을 정해주는 역할을 합니다.

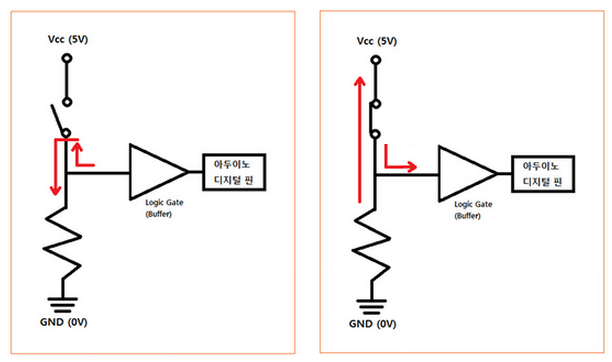

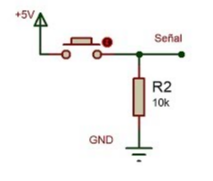

- 풀 업 방식: 아래 (a)는 플로팅 현상이 발생하는 상태일 수 있습니다. (b)는 풀 다운 저항을 적용해 놓았기에(저항을 GND쪽에 연결) 플로팅 상태에서 High Level을 가집니다.

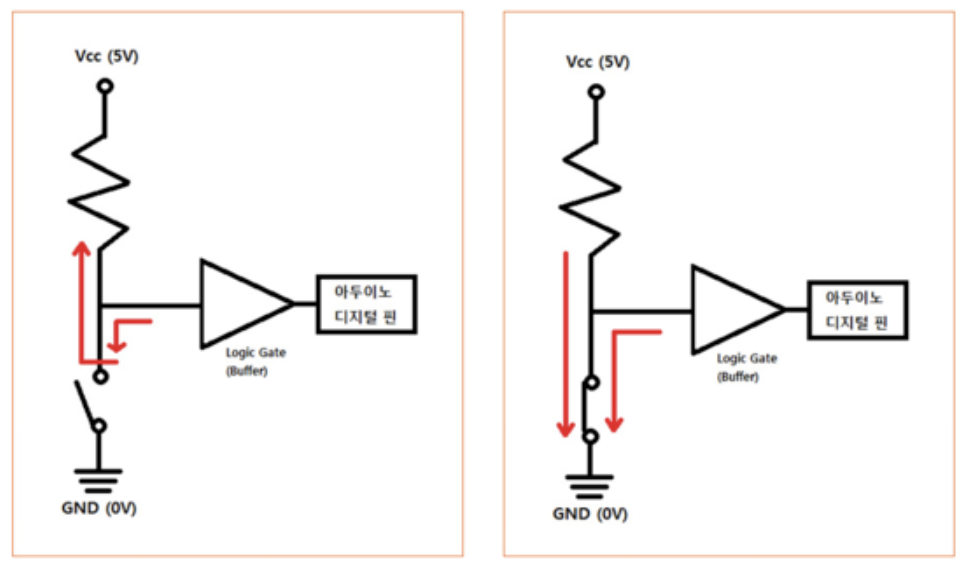

:풀업 저항에서는 풀다운 저항과 달리 Swith가 On 상태에서 제 역할을 다하게 됩니다. 우선 풀업 저항을 사용한 회로에서 Swtich가 Off상태라면 5V연결된 소스에 의해 디지털 회로로 전류가 들어가게 됩니다.

만약 여기서 위에 풀 다운 저항에서 설명한 것처럼 풀 업 저항이 디지털회로에 존재하는 저항 성분보다 커서 전압을 더 많이 갖게되므로 5[V]쪽으로 전류가 흐르지 않냐? 생각할수 있으나 이전에는 소스가 없는 즉, GND에 연결된 경우이고 지금은 5[V]에 연결된 상태입니다. 즉 전압은 풀업 저항도 디지털회로도 아닌 소스쪽이 제일 크기 때문에 소스에서 부터 디지털 회로로 전류가 흐르는 것입니다. 이것만 봐도 Switch Off상태에서 풀업 저항은 큰 의미는 없습니다.

Swith On 상태에서 풀업 저항의 역할이 나오게 됩니다. Swich On 상태에서 스위치 방향의 신호는 5V와 디지털회로 향하는 2가지 경로가 갈리게됩니다. 만약 풀업 저항이 없었다면? 스위치에서의 신호가 5V쪽으로 갈지 디지털 회로로갈지 애매해집니다. 또한 우리가 회로에서 +와 -가 만나면 위험하다는건 모두 알것입니다. 그럼 풀업 저항이 들어가면 5[V]쪽에 연결된 높은 저항값에 의해 디지털회로쪽으로 스위치에서 신호는 모두 디지털 회로로 밀려나게됩니다.

▶3. 회로 구성

- 풀 다운 방식: 풀다운 저항은 입력 핀을 GND와 연결합니다. 스위치나 버튼이 눌리지 않은 상태에서는 입력 핀이 GND에 의해 논리 LOW 상태를 유지합니다. 스위치가 눌리면 입력 핀이 VCC와 연결되어 논리 HIGH 상태가 됩니다.

- 스위치가 눌리지 않은 상태: 입력 핀은 GND를 통해 풀다운 저항에 연결되어 논리 LOW 상태.

- 스위치가 눌린 상태: 입력 핀은 VCC에 연결되어 논리 HIGH 상태.

- 풀 업 방식: 풀업 저항: 입력 핀을 VCC (공급 전압)와 연결합니다. 스위치나 버튼이 눌리지 않은 상태에서는 입력 핀이 VCC에 의해 논리 HIGH 상태를 유지합니다. 스위치가 눌리면 입력 핀이 GND와 연결되어 논리 LOW 상태가 됩니다.

- 스위치가 눌리지 않은 상태: 입력 핀은 VCC를 통해 풀업 저항에 연결되어 논리 HIGH 상태.

- 스위치가 눌린 상태: 입력 핀은 GND에 연결되어 논리 LOW 상태.

▶4. 저항의 크기 결정

실제 아래의 식에 따라서 저항의 크기를 결정하지만 해당 값 들을 찾아내기는 너무 귀찮습니다. 그래서 보통 1kohm 또는 10kohm을 그냥 사용하는 경우가 많습니다.

저항 값 = (공급 전압 – 로직 고전압) / 입력 누설 전류

1. 입력 임피던스(impedance) 고려

- 입력 핀의 임피던스는 해당 핀에 연결된 장치나 마이크로컨트롤러에 따라 다를 수 있습니다.

- 풀업/풀다운 저항의 값은 입력 임피던스와 비슷한 크기로 설정하는 것이 일반적으로 권장됩니다. 예를 들어, 입력 임피던스가 10kΩ인 경우, 풀업/풀다운 저항 값은 주로 10kΩ 정도로 설정됩니다.

2. 전력 소모

- 풀업/풀다운 저항은 전력을 소비합니다. 따라서 전력 소모를 최소화하기 위해 적당한 크기의 저항을 선택해야 합니다.

- 일반적으로 풀업/풀다운 저항의 값은 몇 kΩ에서 몇 십 kΩ 사이에서 선택됩니다. 이 값은 전력 소모와 입력 임피던스에 따라 결정됩니다.

3. 스위치/버튼의 특성 고려

- 스위치나 버튼의 특성도 고려되어야 합니다. 스위치의 닫힘/열림 상태에서 발생하는 바운스 현상 등을 고려하여 풀업/풀다운 저항의 값이 조정될 수 있습니다.

예시

- 대부분의 경우, 풀업/풀다운 저항 값으로 1kΩ에서 100kΩ 사이의 값이 사용됩니다.

- 입력 임피던스가 높은 경우(예: 10kΩ), 풀업/풀다운 저항 값은 일반적으로 10kΩ 정도로 설정됩니다.

- 입력 임피던스가 낮은 경우(예: 1kΩ), 풀업/풀다운 저항 값은 일반적으로 1kΩ보다 큰 값을 선택할 수 있습니다.

풀업/풀다운 저항의 크기를 정할 때는 입력 임피던스, 전력 소모, 스위치/버튼의 특성 등을 고려하여 적절한 값을 선택해야 합니다. 일반적으로 1kΩ에서 100kΩ 사이의 값이 사용되며, 입력 임피던스와 회로의 특성에 따라 조정될 수 있습니다.

이상으로 풀/다운 저항에 대해 마치겠습니다.

감사합니다.

'Digital Circuit' 카테고리의 다른 글

| [ 아두이노 보드 만들기 ] 자작 아두이노 부트로더 올리기 (2) (0) | 2024.07.09 |

|---|---|

| [ 아두이노 보드 만들기 ] 자작 아두이노 만들기 (브레드 보드) (1) (1) | 2024.07.09 |

| [ 아두이노 보드 만들기 ] 아두이노 보드 회로 구성 이해하기 (0) (0) | 2024.07.08 |

| TTL VS CMOS 디지털 논리 레벨 (0) | 2024.06.05 |

| [Quartus] Quartus Tool를 이용한 회로 설계(기본) (0) | 2024.05.06 |

전자공학 블로그에 오신 것을 환영합니다! 최신 기술 동향, 회로 설계, 반도체 및 전자 부품에 대한 유용한 정보와 실습 팁을 제공합니다.

![[ 아두이노 보드 만들기 ] 자작 아두이노 만들기 (브레드 보드) (1)](https://img1.daumcdn.net/thumb/R750x0/?scode=mtistory2&fname=https%3A%2F%2Fblog.kakaocdn.net%2Fdn%2Fbd0fjY%2FbtsIrLMHFl2%2FX21v2xFNpPgYovIvxhEMtk%2Fimg.png)

![[ 아두이노 보드 만들기 ] 아두이노 보드 회로 구성 이해하기 (0)](https://img1.daumcdn.net/thumb/R750x0/?scode=mtistory2&fname=https%3A%2F%2Fblog.kakaocdn.net%2Fdn%2FdJiAxr%2FbtsIrcpYTtT%2FtigMlVZRlmini4g8jqfUuK%2Fimg.png)

![[Quartus] Quartus Tool를 이용한 회로 설계(기본)](https://img1.daumcdn.net/thumb/R750x0/?scode=mtistory2&fname=https%3A%2F%2Fblog.kakaocdn.net%2Fdn%2F6bmlt%2FbtsHd8uTFFx%2FIR6wsPSjSdlgCga9HC4KL0%2Fimg.png)