안녕하세요.

디지털 공학 관점에서 Quartus는 FPGA(Field-Programmable Gate Array) 디자인 및 개발을 위한 강력한 통합 개발 환경입니다. 이를 통해 디지털 시스템을 구현하고 검증하는 데 필요한 다양한 기능과 도구를 제공합니다. 다음은 Quartus를 디지털 공학 관점에서 간략히 설명한 것입니다.

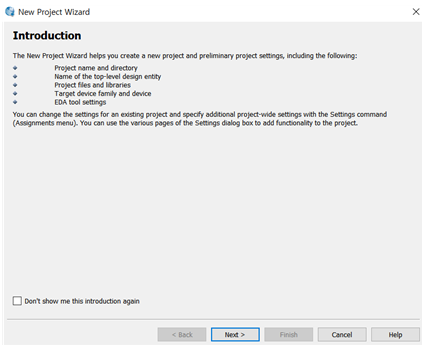

➀ New Project 생성

일반적 과정 ) Next->폴더 지정/프로젝트 네임 지정/Next-> Next -> Family : CycloneII / Available devices : EP2C5AF256A7/ Next->Next->Next->Finish

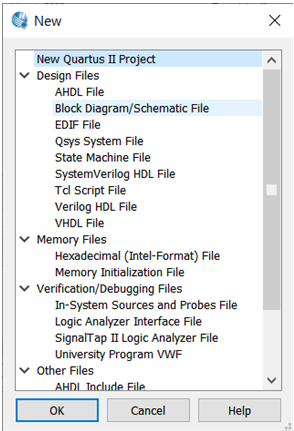

➁ Schematic capture design 생성

( 회로를 직접적으로 설계하는 파일)

과정 ) File/New->Block Diagram/Schematic File->OK

➂ 회로설계, Analysis & Synthesis

( ➁번 파일에 회로를 설계하고, 오류를 검사하는 과정)

과정 ) Symbol Tool, pin Tool과 wire를 통하여 회로설계를 한 이후 'Ctrl+K‘ 혹은 Processing → Start → Start Analysis & Synthesis 클릭

( warning: 수정할 수 있으면 수정하는 것이 좋지만 필수적이지는 않다.

error: 에러가 발생한 부분을 수정하여야 회로가 정상적으로 작동 할 수 없다.)

➃ Vector waveform file 생성

( 파형의 레벨을 적용하는 파일)

과정 ) File/New->University Program VWF->OK

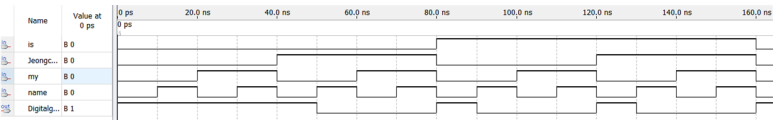

➄ VWF에 입력 단자에 파형의 레벨 입력

과정)

1) VWF파일의 좌측 Name/Value at ps가 적힌 밑 공간 더블 클릭

2) Inset Node or Bus->Node Finder...->List

3) Node Found: 부분의 입출력 핀들을 '>>'을 통해 Selected Node 부분으로 이동 이후, OK 클릭.

4) 상단의 입력레벨 도구들을 통해 비트별로 파형 레벨입력

+) 모든 파형의 경우의 수(ex 2개의 입력 신호의 경우:00,01,10,11)가 다 입력되어야 모든 경우의 수를 파악할 수 있다.

⑥ Simulation

(설계한 회로를 가상 시뮬레이션으로 돌려 결과를 보는 과정)

과정)

1) Simulation → Options -> Quartus Ⅱ Simulator -> OK

2) Simulation – Run Functional Simulation

2) Analtsis & Synthesis 오류 발생시

- 하단에 오류 내용 중 첫 번째 내용을 더블 클릭하면 회로화면의 오류의 부분에 강조가 되므로 수정 후 Analysis & Synthesis를 다시 수행한다.

<오류 중 inst 오류 해결방법>

-"ints"오류는 소자의 이름이 중복되었을 경우 발생한다.

-소자의 이름이 중복된부분을 중복되지 않도록 바꿔준다.

3) 클럭(size of grid)조절하는 방법

- Edit->Grid Size->단위시간 조절

4) 비트 레벨을 Bus로 입력하는 방법

(1) 좌측의 여러개의 입력 핀을 Shift+좌클릭을 통해 중복 클릭하고 해당 위치에서 우클릭

(2) Grouping->Group->Group name 지정->OK

(3) 상단의 Count value->초기값과 변화값 지정->OK

(4) LSB,MSB의 순서를 변경하려면 bus의 name에 우클릭->Reverse Group or Bus bit order 클릭

'Digital Circuit' 카테고리의 다른 글

| [ 아두이노 보드 만들기 ] 자작 아두이노 부트로더 올리기 (2) (0) | 2024.07.09 |

|---|---|

| [ 아두이노 보드 만들기 ] 자작 아두이노 만들기 (브레드 보드) (1) (1) | 2024.07.09 |

| [ 아두이노 보드 만들기 ] 아두이노 보드 회로 구성 이해하기 (0) (0) | 2024.07.08 |

| TTL VS CMOS 디지털 논리 레벨 (0) | 2024.06.05 |

| 풀 업 / 풀 다운 [Pull Up / Pull Down ] 저항 ( 플로팅 원리, 회로 구성 ) (1) | 2024.06.03 |