![[디지털 공학(19)] Latch(래치)와 Flip-flop(플립플롭)_순서논리회로(1)](https://img1.daumcdn.net/thumb/R750x0/?scode=mtistory2&fname=https%3A%2F%2Fblog.kakaocdn.net%2Fdn%2FKZCCD%2FbtsHbPpNlNm%2FJzGOS9d3piqE5y1rqzpHC0%2Fimg.png)

안녕하세요.

이번 시간부터 순서 논리회로에 대해 알아보겠습니다. 우선 가장 기본적이면서 디지털 회로설계에 주요한 래치와 플립플롭에 대해 알아보겠습니다.

순서논리 회로에는 다양한 내용이 있습니다. 필요에 따라 아래 글들도 참고해보세요~!!~

1. Latch(래치)와 Flip-flop(플립플롭)

https://semicircuit.tistory.com/37

2. 비동기 카운터

https://semicircuit.tistory.com/38

3. 동기 카운터

https://semicircuit.tistory.com/39

4. 불규칙 카운터

https://semicircuit.tistory.com/40

5. State Machine 설계

https://semicircuit.tistory.com/41

6. UP/DOWN Counter

https://semicircuit.tistory.com/42

7. 시프트 레지스터

https://semicircuit.tistory.com/43

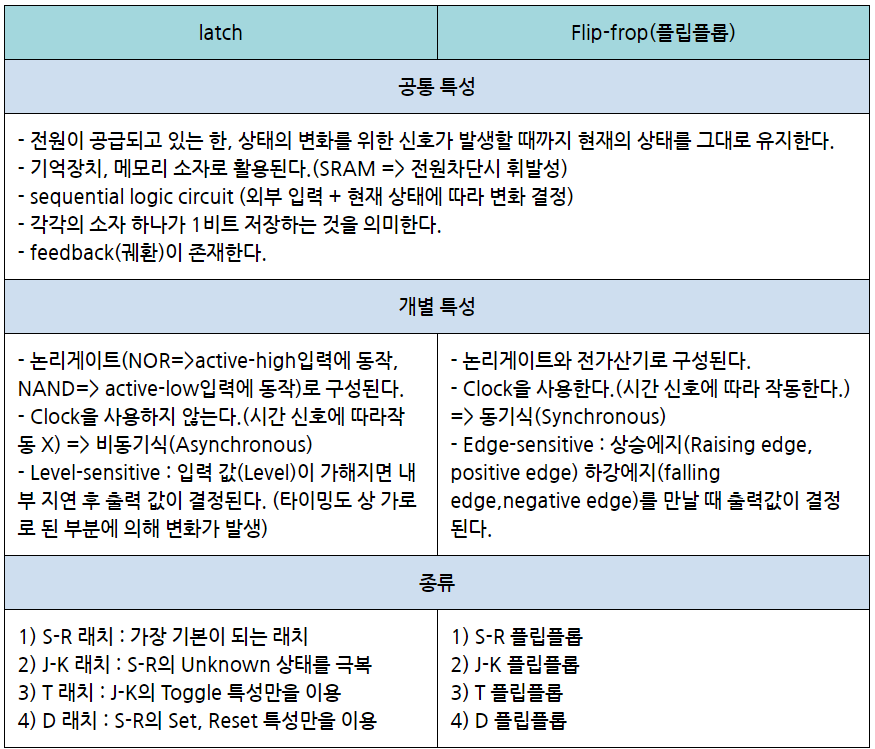

※1. latch(래치)와 Flip-flop(플립플롭)

cf) clock: gate들의 delay로 일정시간의 주기를 갖도록 하는 소자

※2. latch(래치) vs Flip-flop(플립플롭) 차이

1. 데이터 저장 타이밍을 저장하는 신호를 1과 0으로 받으면(Level-sensitive 방식), 정확한 타이밍을 알기 어렵다. 이를 보안하기 위해 0과 1 Level 대신 Risig Edge와 Fallind Edge를 활용하고(Edge-sensitive) 이것을 위해 사용하는 Clock신호는 래치와 클럭의 주된 차이를 가지고 온다. latch(래치)는 Clock(클럭)을 사용하지 않고 Frip-flop(플립플롭)은 Clock(클럭)을 사용한다. Clock의 사용 유무가 원인이 되어 아래의 차이가 발생한다.

2. Level-sensitive 특징에 따라 연속적으로 입력을 확인하고 그에 따른 출력을 변경하며, 플립플롭은 입력을 계속 확인하지만 클럭신호와 대응하는 방식으로 Edge-Sensitive에 따른 Edge(상승,하강)에서 출력을 변경한다. (즉, 트리거 방식의 차이)

3. 구성의 부분에서 latch(래치)는 논리게이트의 조합으로 회로를 구성하는데 Frip-flop(플립플롭)은 클록 신호와 래치를 조합하여 구성된다.

4. latch(래치)는 비동기식(Asynchronous)신호이고 입력신호만 사용하여 입력개수=입력신호 이지만 Flip-frop(플립플롭)은 동기식(Synchronous)신호이고 입력신호와 clock신호를 사용하여 입력개수=입력신호+clock신호이다.

5. 결론적으로 래치는 클럭신호가 없어 레지스터로 사용할 수 없다. 그러나 플립플롭은 함께 레지스터로 작동 할 수 있다.

※3. latch(래치)의 종류

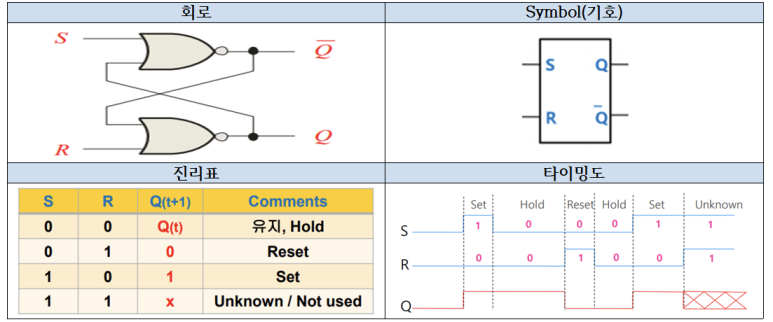

▶1. S-R Latch

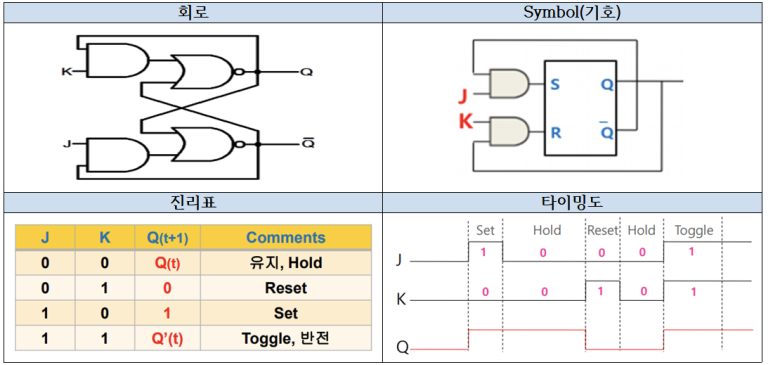

▶2. J-K Latch

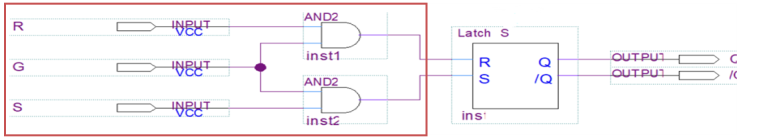

cf) 다음처럼 래치 앞에 gate회로를 통해 1때는 정상적인 동작, 0일 때는 무조건 Hold하는 회로를 구상할 수 있다.

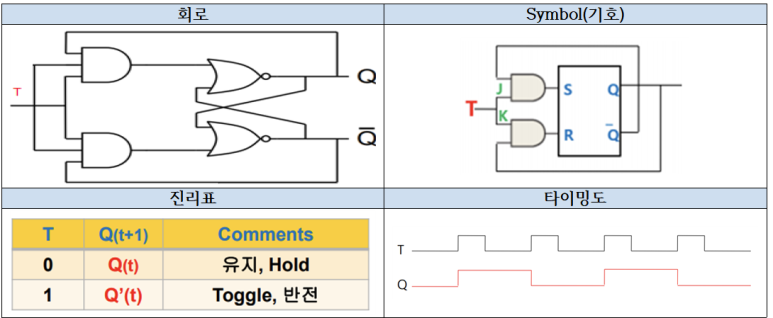

▶3. T Latch

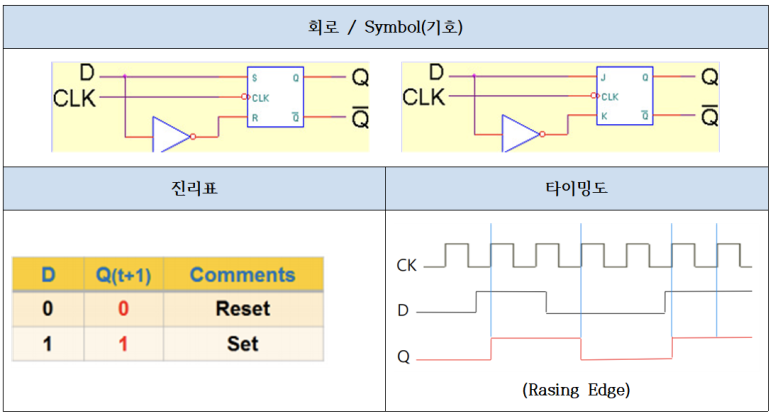

▶4. D Latch

cf) Comments

⓵ Hold/유지 : Q의 이전의 출력 상태 기억 (초기상태는 Q=0)

⓶ Set : Q=1인 상태

⓷ Reset : Q=0인 상태

⓸ Unknown/Not used : 존재 할수 없는 상태(에러)

⓹ Toggle/반전 : Q의 이전의 출력 상태를 반전해서 기억

※4. Flip-flop의 종류

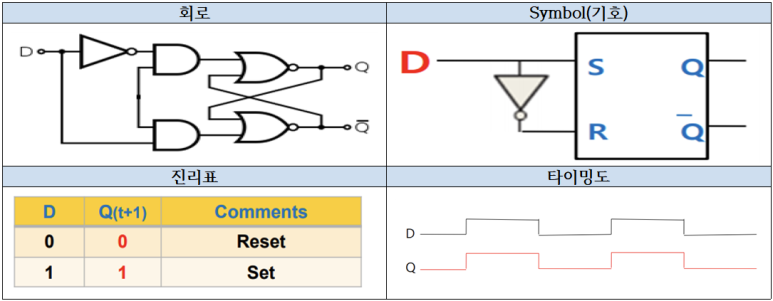

▶1. S-R Flipflop

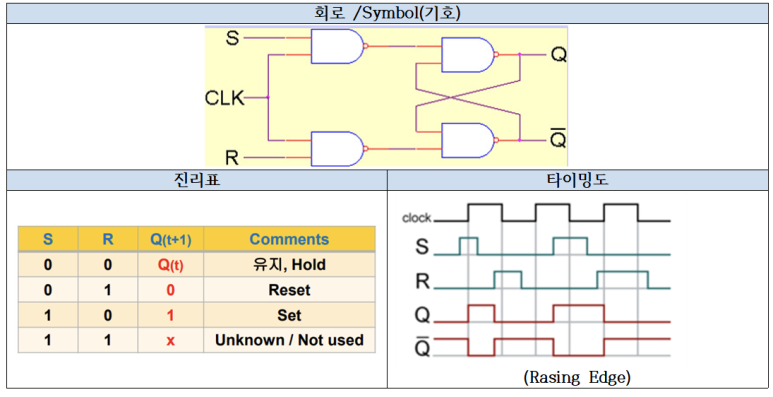

▶2. J-K Flipflop

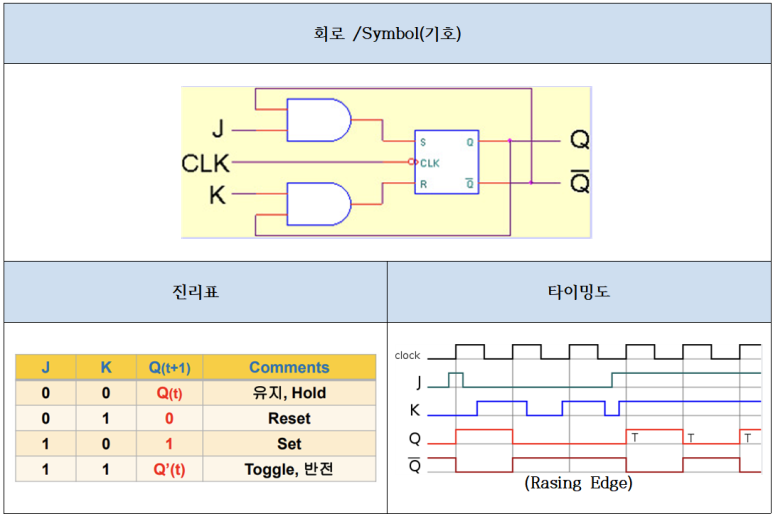

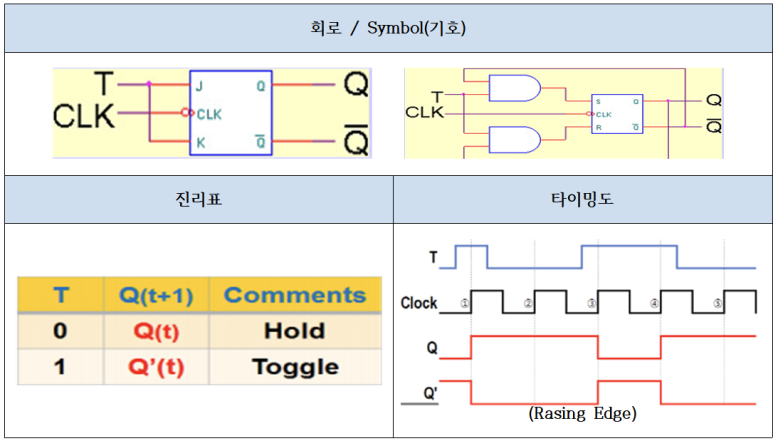

▶3. T Flipflop

▶3. T Flipflop

cf) CLK에 버블이 붙지 않으면 rasing Edge Triggering

CLK에 버블이 붙으면 Falling Edge Triggering

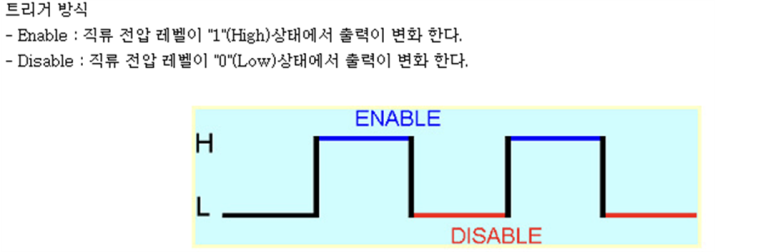

※5. 트리거 방식(Tringging)

▶1. 래치의 트리거 방식

입력 EN에 버블이 붙으면 DIsable(Low level Triggering), 붙지 않으면 ENABLE(High level Triggering)

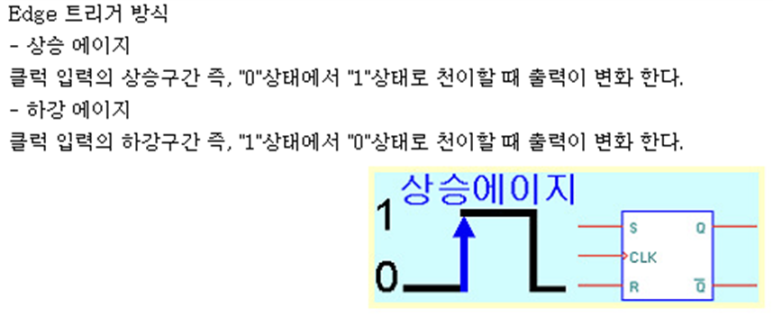

▶2. 플립플롭의 트리거 방식

입력 CLK에 버블이 붙으면 하강 에이지(Negative Edge Triggering, CLK에 버블이 붙지 않으면 상승 에이지(Positive Edge Triggering)

Solution||

1) 데이터 저장 타이밍을 저장하는 신호를 1과 0으로 받으면(Level-sensitive 방식), 정확한 타이밍을 알기 어렵다. 이를 보안하기 위해 0과 1 Level 대신 Risig Edge와 Falling Edge를 활용하고(Edge-sensitive) 이것을 위해 사용하는 Clock신호는 래치와 클럭의 주된 차이를 보여주게 한다. latch(래치)는 Clock(클럭)을 사용하지 않고 Frip-flop(플립플롭)은 Clock(클럭)을 사용한다. Clock의 사용 유무가 원인이 되어 아래의 차이가 발생한다.

2) Level-sensitive 특징에 따라 연속적으로 입력을 확인하고 그에 따른 출력을 변경하며, 플립플롭은 입력을 계속 확인하지만 클럭신호와 대응하는 방식으로 Edge-Sensitive에 따른 Edge(상승,하강)에서 출력을 변경한다.

3) 구성의 부분에서 latch(래치)는 논리게이트의 조합으로 회로를 구성하는데

Frip-flop(플립플롭)은 클록 신호와 래치를 조합하여 구성된다.

4) latch(래치)는 비동기식(Asynchronous)신호이고 입력신호만 사용하여 입력개수=입력신호 이지만 Flip-frop(플립플롭)은 동기식(Synchronous)신호이고 입력신호와 clock신호를 사용하여 입력개수=입력신호+clock신호이다.

5) 결론적으로 래치는 클럭신호가 없어 레지스터로 사용할 수 없다. 그러나 플립플롭은 함께 레지스터로 작동 할 수 있다.

'University curriculum > [Course] Digital Engineering' 카테고리의 다른 글

전자공학 블로그에 오신 것을 환영합니다! 최신 기술 동향, 회로 설계, 반도체 및 전자 부품에 대한 유용한 정보와 실습 팁을 제공합니다.

![[디지털 공학(21)] Synchronism Counter(동기 카운터)_순서논리회로(3)](https://img1.daumcdn.net/thumb/R750x0/?scode=mtistory2&fname=https%3A%2F%2Fblog.kakaocdn.net%2Fdn%2FdiVKAa%2FbtsHcoFeVm4%2FKSPFtyYiAD12XQnKdVvylk%2Fimg.png)

![[디지털 공학(20)] Asynchronism Counter(비동기 카운터)_순서논리회로(2)](https://img1.daumcdn.net/thumb/R750x0/?scode=mtistory2&fname=https%3A%2F%2Fblog.kakaocdn.net%2Fdn%2FbTDfAk%2FbtsHbusMXz8%2FkyITe1rRIjKH9wlOX6HPHk%2Fimg.png)

![[디지털 공학(18)] 패리티 발생기/검사기(Paity Detector) _조합논리회로(6)](https://img1.daumcdn.net/thumb/R750x0/?scode=mtistory2&fname=https%3A%2F%2Fblog.kakaocdn.net%2Fdn%2FK5RY6%2FbtsHbvd1aso%2F0dSy2ajhkJlL7slmlsJsP1%2Fimg.png)

![[디지털 공학(17)] Code Converters (부호 변환기) - Gray Code(<->2진수), ASCII Code(<->2진,8진,10진,16진수)_조합논리회로(5)](https://img1.daumcdn.net/thumb/R750x0/?scode=mtistory2&fname=https%3A%2F%2Fblog.kakaocdn.net%2Fdn%2FUPtEV%2FbtsHdxBJIAd%2FHF4KppTr4vfpoWtO6kC1F0%2Fimg.png)