![[반도체 공정] Moore's Law & Huang's Law (무어의 법칙 & 황의 법칙)](https://img1.daumcdn.net/thumb/R750x0/?scode=mtistory2&fname=https%3A%2F%2Fblog.kakaocdn.net%2Fdn%2F9bs38%2FbtsHm0jUuqe%2FvwPRnKIXJ2FakcRVkexqy0%2Fimg.png)

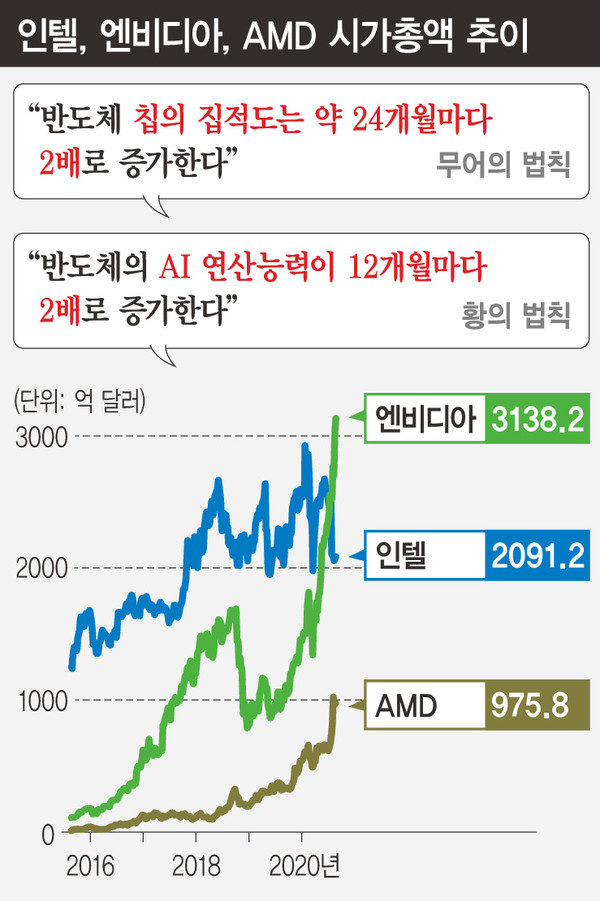

반도체 발전은 무어의 법칙과 같은 기술적인 발전과 함께, 황의 법칙과 같은 새로운 트렌드의 등장으로 이뤄지고 있습니다.. 무어의 법칙은 집적도의 지수적 증가를, 황의 법칙(NDIVIA)은 GPU의 성능 증가를 강조하며, 이러한 발전은 현대 기술 분야에서 빠른 진보를 이끌어내고 있다.

이번 게시글에서는 무어의 법칙과 NDIVIA의 황의 법칙, 그리고 추가적으로 삼성의 황의 법칙에 대해 알아보려고 합니다.

※1. Moore's Law

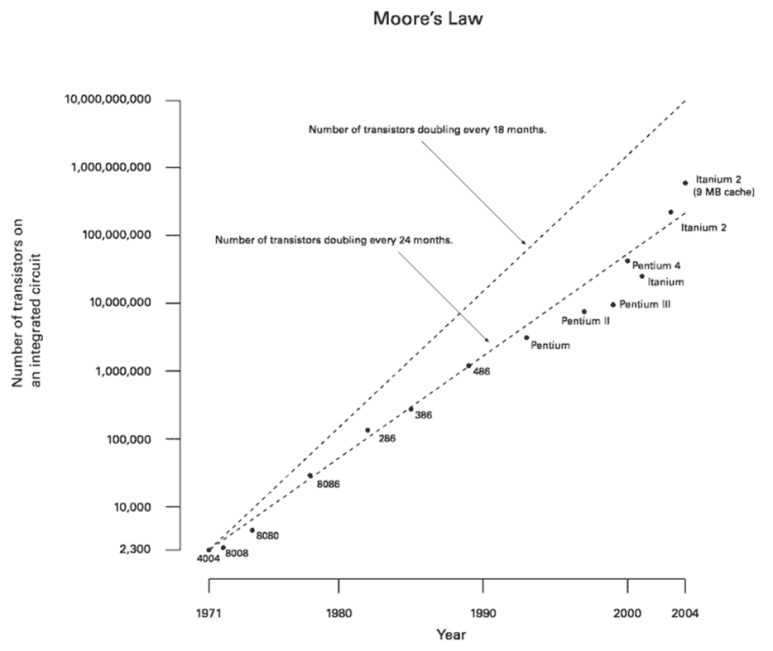

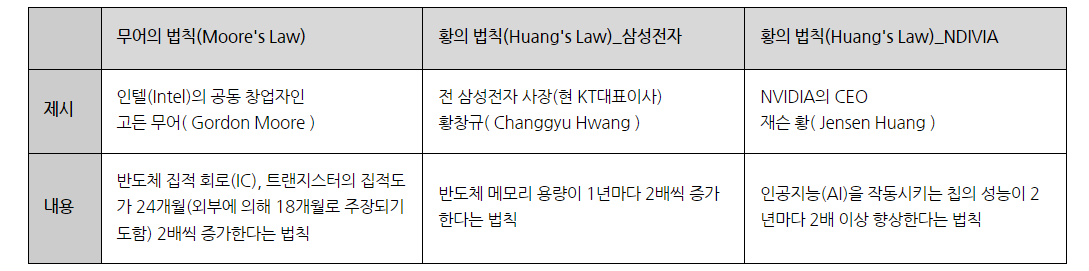

무어의 법칙(Moore's Law)은 반도체 산업에서 매우 중요한 법칙 중 하나이다. 이 법칙은 인텔(Intel)의 공동 창업자인 고든 무어(Gordon Moore)가 1965년에 발표한 연구 결과에서 시작되었다.

무어의 법칙은 두 가지 주요 요소로 구성되어 있다. 첫 번째 요소는 년도와 함께 집적도(Integration Density)가 높아지는 것이다. 집적도란 반도체 칩에 포함된 트랜지스터의 개수를 말한다. 두 번째 요소는 년도와 함께 반도체 칩의 가격이 하락하는 것이다.

무어의 법칙은 초창기에는 1년에 트랜지스터가 두 배로 증가하며, 이후 10년후에는 2년에 두 배로 정정하였으며 현재는 인텔의 임원직인 데이비드 하우스 대략 18개월마다 두 배씩 증가한다는 것으로 정정 되어 현재 가장 많이 알려졌습니다.

하지만, 최근에는 공정의 한계와 열 관리 등의 문제로 인해 모어의 법칙이 이전만큼 더이상 적용되지 않는 것으로 판단되고 있다. 따라서, 새로운 기술과 아키텍처가 필요하게 되었으며, 예를 들어 3D 집적회로 및 새로운 소자 기술 등이 연구되고 있다.

※2. 삼성의 Huang's Law

전 삼성전자 창업자 황창규의 Huang's Law는 "2년마다 메모리 반도체 용량이 2배씩 증가한다"는 법칙이다.

이러한 삼성의 황의 법칙은 메모리 반도체 기술의 발전 속도를 보여주는 지표로 사용된다. 이 법칙은 메모리 용량 증가의 예측과 함께, 메모리 가격 하락, 성능 개선 등을 이끌어내는 중요한 역할을 한다.

최근에는 황의 법칙에 따라 3D NAND와 HBM(High Bandwidth Memory) 등의 새로운 메모리 기술이 출시되면서, 메모리 용량과 성능의 개선이 더욱 가속화되고 있다.

※3. 엔디비아의 Huang's Law

엔비디아 황의 법칙'은 인공지능(AI)을 작동시키는 실리콘칩의 성능이 2년마다 2배 이상 향상한다는 법칙이다. 이 법칙은 미국 반도체 기업 엔비디아의 공통 창업자이자 최고경영자(CEO)인 젠슨 황이 주창한 것이다.

엔비디아는 반도체 집적도가 2년마다 2배씩 증가한다는 경험칙인 '무어의 법칙'이 제조업 시대에 맞춘 것이라고 지적하면서 AI 시대를 맞아 새로운 법칙인 황의 법칙을 따라야 할 때라고 선언했다.

무어의 법칙은 1965년 제시된 후 반도체 산업의 발달을 잘 예측해 왔지만, 반도체 칩의 집적도를 높이는 초미세 공정 기술이 발달하면서 추가 개선이 물리적으로 어려워진 데다 칩 집적도보다 AI 처리능력이 더 중요하다 주장했다.

※4. Moore's Law의 한계와 그에 따른 패키징의 중요성

반도체 제조 기술의 발전은 무어의 법칙에 의해 예측되었지만, 이젠 공정의 한계로 인해 더 이상 집적도를 높이기 위한 칩 설계 및 제조 기술에 한계가 있는 상황이다. 이러한 상황에서 반도체 패키징 기술은 더욱 중요해지고 있다.

공정의 한계는 반도체 칩 내부의 구성요소를 만들어내는 기술의 한계를 의미한다. 더 이상 반도체 칩의 집적도를 높이기 위한 공정 기술의 발전이 어려워지고 있기 때문에, 반도체 패키징 기술은 더욱 중요한 역할을 하게 되었다. 패키징 기술은 칩의 외부 환경으로부터 보호하고, 칩과 다른 장치들 간의 연결을 가능케 하며, 칩의 안정성과 신뢰성을 보장하는 역할을 한다.

따라서, 반도체 패키징 기술은 공정의 한계로 인해 무어의 법칙이 더 이상 유효하지 않아지는 상황에서도 중요한 역할을 하고 있다. 공정의 한계를 극복하기 위한 패키징을 방법 중에는 소자의 구조의 변화가 있고 대표적으로 트랜지스터가 (PlanarFET - FinFET - GAAFER - MBCFET) 같은 구조 변화로 게이트 단면적을 효과적으로 넓힌다.

'Semiconductor > Semiconductor Fabrication' 카테고리의 다른 글

| [반도체 공정] 노광 공정, 노광 장비 (2) | 2024.05.16 |

|---|---|

| [반도체 공정] RAM / NAND Flash / 시스템반도체 (1) | 2024.05.15 |

| [반도체 공정] 플라즈마 공정, 플라즈마 장비 (2) | 2024.05.15 |

| [반도체 공정] 이온 주입 공정, 이온 주입 장비 (0) | 2024.05.14 |

| [반도체 공정] 패키징 공정, 패키징 장비 (0) | 2024.05.14 |

전자공학 블로그에 오신 것을 환영합니다! 최신 기술 동향, 회로 설계, 반도체 및 전자 부품에 대한 유용한 정보와 실습 팁을 제공합니다.

![[반도체 공정] 노광 공정, 노광 장비](https://img1.daumcdn.net/thumb/R750x0/?scode=mtistory2&fname=https%3A%2F%2Fblog.kakaocdn.net%2Fdn%2F57v6a%2FbtsHmZk1TVr%2FBmPz0h7wp5Di8XkVlSmtyk%2Fimg.png)

![[반도체 공정] RAM / NAND Flash / 시스템반도체](https://img1.daumcdn.net/thumb/R750x0/?scode=mtistory2&fname=https%3A%2F%2Fblog.kakaocdn.net%2Fdn%2FRMvfg%2FbtsHl3vc4jU%2FtOeDfzJEnZOubBbFYNcFHk%2Fimg.png)

![[반도체 공정] 플라즈마 공정, 플라즈마 장비](https://img1.daumcdn.net/thumb/R750x0/?scode=mtistory2&fname=https%3A%2F%2Fblog.kakaocdn.net%2Fdn%2FWX2pn%2FbtsHnstvyJw%2FZpdeOPNZ9P6RfZcFUliY80%2Fimg.png)

![[반도체 공정] 이온 주입 공정, 이온 주입 장비](https://img1.daumcdn.net/thumb/R750x0/?scode=mtistory2&fname=https%3A%2F%2Fblog.kakaocdn.net%2Fdn%2FcckysS%2FbtsHmBSxnBc%2FfzvkHwHhWEzESNOCCOlC00%2Fimg.png)