![[Verilog] wire와 reg 차이점 완벽 정리](https://img1.daumcdn.net/thumb/R750x0/?scode=mtistory2&fname=https%3A%2F%2Fblog.kakaocdn.net%2Fdn%2Fbmzzf6%2FbtsMvf25EcW%2F0q5KRIANaHY9KMKTDlv0TK%2Fimg.jpg)

안녕하세요.

Verilog에서 가장 많이 사용되는 데이터 타입은 **wire와 reg**입니다. 두 타입 모두 디지털 회로 설계에서 중요한 역할을 하지만, 개념과 동작 방식에서 차이가 있습니다.

많은 초보 설계자들이 "wire와 reg의 차이가 무엇인지?", "어떤 경우에 wire를 쓰고, 어떤 경우에 reg를 써야 하는지?" 헷갈려하는 경우가 많습니다. 이번 글에서는 wire와 reg의 개념, 차이점, 그리고 사용 예제를 정리해보겠습니다.

※1. wire와 reg의 기본 개념

Verilog에서 wire와 reg의 가장 큰 차이는 값을 저장하는 방식입니다.

- wire는 실제 하드웨어의 배선(Wiring)과 같은 역할을 하며, 직접 값을 저장할 수 없습니다. 대신, assign 문이나 게이트 출력과 연결됩니다.

- reg는 플립플롭(Flip-Flop)처럼 값을 저장하는 역할을 하며, 클럭 신호(always 블록)와 함께 동작합니다.

| 데이터 타입 | 설명 | 값 저장 여부 | 사용 위치 |

| wire | 물리적 배선(연결선) | 저장 불가능 | 조합 논리(Combinational Logic) |

| reg | 값 저장용 변수 | 값 저장 가능 | 순차 논리(Sequential Logic) |

cf) 값을 저장한다??

Verilog에서 "값을 저장한다"는 의미는 이전 상태를 유지할 수 있는지 여부를 뜻합니다.

✅ wire는 값을 저장하지 않는다

- wire는 물리적인 배선 역할만 하기 때문에, 현재 입력된 신호를 즉시 반영할 뿐 이전 값을 기억하지 못합니다.

- 따라서, assign을 통해 즉시 계산된 결과만 전달할 수 있습니다.

예제 1: wire는 값이 유지되지 않음

- c는 항상 a & b의 값과 동일하게 유지됩니다.

- 만약 a 또는 b가 바뀌면 c도 즉시 바뀌며, 이전 값은 사라집니다.

- 즉, c는 이전 값을 저장하지 않습니다.

✅ reg는 값을 저장한다

- reg는 클럭 신호를 기반으로 값이 변경될 때까지 유지됩니다.

- 즉, 한 번 설정된 값은 다음 클럭 신호가 오기 전까지 변하지 않고 저장됩니다.

예제 2: reg는 이전 값을 유지할 수 있음

- d의 값이 변하더라도, clk가 상승할 때까지 q의 값은 변하지 않습니다.

- 클럭 신호가 입력되었을 때만 q가 새로운 값으로 업데이트되므로, 이전 값이 유지됩니다.

※2. wire의 특징과 사용법

▶1. wire의 개념

wire는 물리적인 연결선을 의미하며, 입력 신호를 다른 곳으로 전달하는 역할을 합니다. 직접 값을 저장할 수 없으며, 항상 assign문이나 게이트 출력에 의해 값이 설정됩니다.

▶2. wire 선언

wire a; // 단일 비트 wire 선언

wire [7:0] data; // 8비트 벡터 wire 선언

▶3. wire 사용 예제

(1) assign을 이용한 조합 논리

- assign을 사용하여 논리 연산을 수행할 수 있음

- c는 a와 b의 AND 연산 결과를 실시간으로 반영

wire a, b, c; assign c = a & b; // a와 b의 AND 연산 결과가 c에 할당됨

(2) 게이트 모델링

- wire 타입을 사용하여 논리 게이트를 연결

wire a, b, y;

and U1 (y, a, b); // AND 게이트 사용

(3) 다중 드라이버 지원 (tri)

- wire는 기본적으로 하나의 소스에서 값을 받아야 하지만, tri는 다중 드라이버를 지원

tri bus; // 3-state 버스를 위한 tri 선언

※3. reg의 특징과 사용법

▶1. reg의 개념

reg는 값을 저장할 수 있는 변수로, 클럭 신호를 기반으로 동작하는 순차 논리 회로에서 주로 사용됩니다.

- always 블록 내부에서만 값을 변경할 수 있음

- 클럭(edge-triggered) 이벤트와 함께 동작하여 데이터를 저장

▶2. reg 선언

reg a; // 단일 비트 변수

reg [7:0] data; // 8비트 변수

▶3. reg 사용 예제

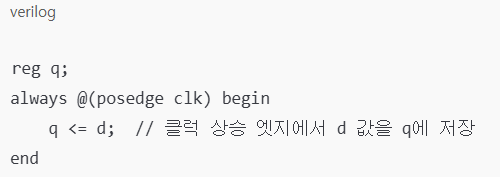

(1) 플립플롭 동작 구현 (클럭 기반 동작)

- always 블록 내부에서 reg 변수는 값이 변경될 수 있음

- 클럭 신호(posedge clk)가 발생할 때마다 d의 값이 q에 저장됨

reg q;

always @(posedge clk) begin

q <= d; // 클럭 상승 엣지에서 d 값을 q에 저장

end

(2) 카운터 구현

- reg 타입을 사용하여 4비트 카운터 구현 가능

reg [3:0] count;

always @(posedge clk) begin

count <= count + 1; // 클럭이 올라갈 때마다 count 증가

end

(3) 초기값 설정 (initial)

- reg 변수는 initial 블록에서 초기화 가능

reg [7:0] data;

initial begin

data = 8'b10101010; // 시뮬레이션 초기값 설정

end

※4. wire vs reg 비교

< wire와 reg 선택 기준>

=> 조합 논리 회로(즉각적인 논리 연산) → wire 사용

=> 순차 논리 회로(클럭 기반 동작) → reg 사용

| 비교 항목 | wire | reg |

| 값 저장 가능 여부 | 값 저장 불가 | 값 저장 가능 |

| 사용 위치 | 조합 논리(Combinational Logic) | 순차 논리(Sequentail Logic) |

| 값 할당 방식 | assign 또는 게이트 출력 | alway, initial 블록 내부에서만 변경 가능 |

| 클럭 신호 필요 여부 | 없음 | 있음 |

| 예제 | assign y = a & b; | always @(posedge clk) q <= d; |

<요약>

1) wire는 조합 논리에서 사용

- 배선 역할을 하며 값을 저장하지 않음

- assign문 또는 게이트 연결에 사용됨

- 클럭 신호 없이 실시간 값 반영

2) reg는 순차 논리에서 사용

- 값 저장이 가능하며 always 블록 내부에서 변경됨

- 클럭 신호(posedge clk)와 함께 동작

- 플립플롭, 카운터 등의 저장 장치 설계에 사용됨

이상으로 Verilog의 데이터 타입중 대표되는 reg와 wire에 대해 마치겠습니다. 감사합니다.

'Digital Circuit > HDL(Verilog, VHDL)' 카테고리의 다른 글

| [Verilog] if문과 case문 형태 (0) | 2025.03.01 |

|---|---|

| [Verilog] assign, initial, always문의 차이 (0) | 2025.03.01 |

| [Verilog] 연속할당문(Continuous Assignment) VS 절차할당문(Procedural Assignment)의 차이 (0) | 2025.02.26 |

| [Verilog] "="(blocking)과 "<="(non-blocking) 할당의 차이 (0) | 2025.02.25 |

| Verilog vs VHDL: 차이점과 특징 비교 (1) | 2025.02.24 |

전자공학 블로그에 오신 것을 환영합니다! 최신 기술 동향, 회로 설계, 반도체 및 전자 부품에 대한 유용한 정보와 실습 팁을 제공합니다.

![[Verilog] "="(blocking)과 "<="(non-blocking) 할당의 차이](https://img1.daumcdn.net/thumb/R750x0/?scode=mtistory2&fname=https%3A%2F%2Fblog.kakaocdn.net%2Fdn%2FmcRTA%2FbtsMsO0sdLk%2FBlJkDRkiPG2g8YapsGNN01%2Fimg.png)