안녕하세요.

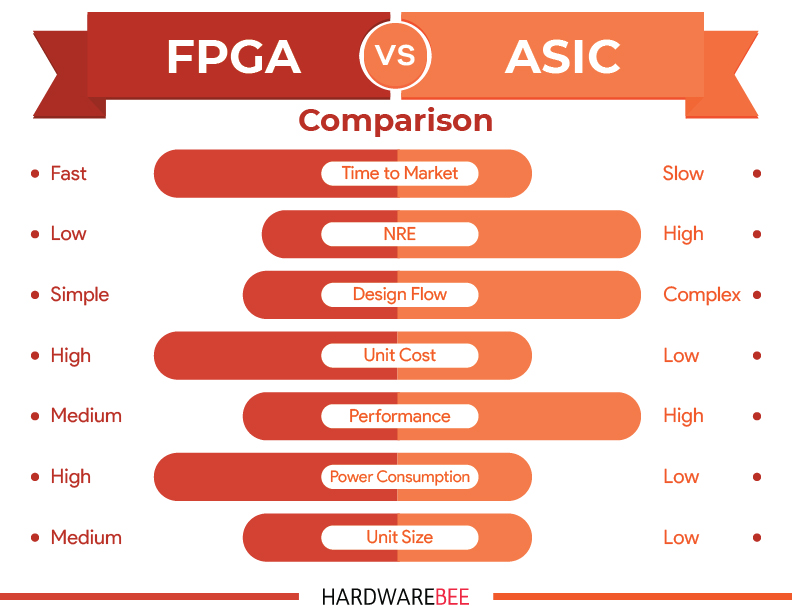

디지털 회로 설계에서 가장 널리 사용되는 두 가지 하드웨어 기술 언어(HDL, Hardware Description Language)는 Verilog와 VHDL입니다. 둘 다 FPGA(Field Programmable Gate Array) 및 ASIC(Application-Specific Integrated Circuit) 설계에 사용되지만, 문법과 사용 방식에서 큰 차이가 있습니다. 이번 글에서는 Verilog와 VHDL의 주요 차이를 비교하고, 각각의 장단점을 살펴보겠습니다.

※1. Verilog?

▶1. Verilog란?

Verilog는 1984년 Gateway Design Automation에서 개발한 하드웨어 기술 언어로, 이후 1995년 IEEE 1364 표준으로 채택되었습니다. 문법이 C 언어와 유사하여 비교적 배우기 쉽고, 디지털 회로를 효율적으로 설계할 수 있습니다.

▶2. 특징

- C 언어와 유사한 문법 → 프로그래머가 쉽게 적응 가능

- 비교적 간결한 코드 구조 → 빠른 설계 및 디버깅 가능

- 시뮬레이션 및 합성에 최적화 → ASIC 및 FPGA 설계에서 많이 사용됨

※2. VHDL?

▶1. VHDL이란?

VHDL(VHSIC Hardware Description Language)은 미국 국방부의 VHSIC(Very High-Speed Integrated Circuit) 프로젝트에서 개발한 언어로, 1987년 IEEE 1076 표준으로 제정되었습니다. Verilog에 비해 문법이 복잡하지만, 강력한 데이터 타입과 구조적인 설계가 가능합니다.

▶2. 특징

- Ada 및 Pascal과 유사한 문법 → 엄격한 형식 사용

- 강력한 데이터 타입 지원 → 다양한 논리 연산 및 시뮬레이션 가능

- 신뢰성이 높고 구조적인 설계 가능 → 산업 및 항공우주 분야에서 많이 사용됨

※3. 문법 비교

▶1. 변수 선언 방식

Verilog와 VHDL의 변수 선언 방식은 큰 차이가 있습니다.

🔹 Verilog 예제

: Verilog에서는 reg와 wire를 사용하여 변수를 선언

reg [7:0] data; // 8비트 레지스터 선언

wire clk; // 클록 신호

🔹 VHDL 예제

: VHDL에서는 signal과 variable을 사용하며, 데이터 타입을 명확히 지정해야 함

signal data : std_logic_vector(7 downto 0); -- 8비트 신호 선언

signal clk : std_logic; -- 클록 신호▶2. 프로세스 및 동작 방식

🔹 Verilog의 Always 블록

- always 블록을 사용하여 클럭 상승 엣지(posedge clk)에서 동작

- 비동기 및 동기 논리를 쉽게 구현 가능

always @(posedge clk) begin

data <= data + 1;

end

🔹 VHDL의 Process 블록

- process 블록을 사용하여 논리 실행

- rising_edge(clk) 함수를 사용하여 클럭 상승 엣지를 감지

process (clk)

begin

if rising_edge(clk) then

data <= data + 1;

end if;

end process;

▶3. 병렬 구조 및 순차 구조

🔹 Verilog 병렬 실행 예제

: Verilog는 always 블록을 이용하여 순차 및 병렬 처리를 혼합하여 구현합니다.

assign sum = a + b; // 병렬 실행

assign diff = a - b;

🔹 VHDL 병렬 실행 예제

: VHDL은 병렬 실행을 기본으로 하고, 순차 실행이 필요할 때 process 블록을 사용합니다.

sum <= a + b; -- 병렬 실행

diff <= a - b;

※4. 주요 차이점 비교

| 비교 항목 | Verilog | VHDL |

| 개발 연도 | 1984년 | 1987년 |

| 표준화 | IEEE 1364 | IEEE 1076 |

| 문법 스타일 | C 언어 유사 | Ada/Pascal 유사 |

| 데이터 타입 | 단순, wire, reg | 엄격, std_logic_vector 사용 |

| 코드 가독성 | 짧고 직관적 | 구조적이지만 복잡함 |

| 사용 분야 | FPGA, ASIC 설계 | 방산, 항공우주, 산업 자동화 |

| 병렬 처리 방식 | assign, always 블록 사용 | process 블록 기본 |

| 합성 최적화 | 빠른 합성 | 강력한 설계 검증 |

| 신뢰성 | 빠르지만 오류 가능성 있음 | 강력한 타입 체크로 높은 신뢰성 |

※5. Verilog vs. VHDL: 언제 사용해야 할까?

▶1. Verilog가 적합한 경우

- FPGA 및 ASIC 설계를 빠르게 해야 할 때

- C 기반 개발 환경에 익숙한 엔지니어

- 간단한 논리 설계 및 신속한 시뮬레이션이 필요한 경우

▶2. VHDL이 적합한 경우

- 신뢰성이 중요한 방산, 항공우주, 자동차 산업

- 복잡한 데이터 타입과 강력한 구조적 설계가 필요한 경우

- 엄격한 검증과 높은 품질의 설계가 필요한 프로젝트

Verilog와 VHDL은 각각의 강점이 있으며, 프로젝트의 성격에 따라 선택하는 것이 중요합니다. Verilog는 빠른 개발과 가독성에 초점이 맞춰져 있고, VHDL은 신뢰성과 정형화된 설계에 강점이 있습니다.

FPGA 및 디지털 회로 설계를 배우고자 한다면, 두 언어를 모두 익혀 두는 것이 유리합니다. 특히 VHDL은 구조적 설계를 이해하는 데 도움이 되고, Verilog는 빠른 구현과 테스트에 유용합니다. 자신이 목표로 하는 분야와 프로젝트 요구사항을 고려하여 적절한 언어를 선택하면 좋겠습니다.

이상으로 VHDL과 Verilog의 차이에 대해 마치겠습니다. 감사합니다.

'Digital Circuit > HDL(Verilog, VHDL)' 카테고리의 다른 글

| [Verilog] if문과 case문 형태 (0) | 2025.03.01 |

|---|---|

| [Verilog] assign, initial, always문의 차이 (0) | 2025.03.01 |

| [Verilog] 연속할당문(Continuous Assignment) VS 절차할당문(Procedural Assignment)의 차이 (0) | 2025.02.26 |

| [Verilog] "="(blocking)과 "<="(non-blocking) 할당의 차이 (0) | 2025.02.25 |

| [Verilog] wire와 reg 차이점 완벽 정리 (0) | 2025.02.24 |

전자공학 블로그에 오신 것을 환영합니다! 최신 기술 동향, 회로 설계, 반도체 및 전자 부품에 대한 유용한 정보와 실습 팁을 제공합니다.

![[Verilog] "="(blocking)과 "<="(non-blocking) 할당의 차이](https://img1.daumcdn.net/thumb/R750x0/?scode=mtistory2&fname=https%3A%2F%2Fblog.kakaocdn.net%2Fdn%2FmcRTA%2FbtsMsO0sdLk%2FBlJkDRkiPG2g8YapsGNN01%2Fimg.png)

![[Verilog] wire와 reg 차이점 완벽 정리](https://img1.daumcdn.net/thumb/R750x0/?scode=mtistory2&fname=https%3A%2F%2Fblog.kakaocdn.net%2Fdn%2Fbmzzf6%2FbtsMvf25EcW%2F0q5KRIANaHY9KMKTDlv0TK%2Fimg.jpg)