![[디지털 공학(13)] 조합논리의 기능(반가산기, 전가산기 설계 // 덧셈기, 덧뺄셈기) _ 조합논리회로 (1)](https://img1.daumcdn.net/thumb/R750x0/?scode=mtistory2&fname=https%3A%2F%2Fblog.kakaocdn.net%2Fdn%2FbupB76%2FbtsHed35Ljo%2F7LXgMKrS3XCp4v2kCNJRT1%2Fimg.png)

안녕하세요.

이번 포스트에서는 지난 포스트에서 다루었던 논리연산의 내용들을 바탕으로 반가산기, 전가산기에 대해 배우고 이를 가지고 덧셈기(덧셈만 가능)와 덧뺄셈기(덧셈, 뺄셈 모두 가능) Quartus Tool을 기반으로 설계하는 과정을 진행하겠습니다.

조합논리 회로에 대해 추가적인 내용으로 아래 포스트를 참조해 주세요~!~

1. 조합논리 회로 VS 순서논리 회로

https://semicircuit.tistory.com/29

2. 전가산기, 반가산기, 덧셈기, 뺄셈기

https://semicircuit.tistory.com/31

3. 비교기

https://semicircuit.tistory.com/32

4. 디코더, 인코더

https://semicircuit.tistory.com/33

5. 멀티플렉서, 디멀티플렉서

https://semicircuit.tistory.com/34

6. 부호변환기 ( 2진수-그레이코드, ASCII 코드)

https://semicircuit.tistory.com/35

7. 패리티 발생기/검사기

https://semicircuit.tistory.com/36

!!본문 내용은 디지털 회로설계 및 시뮬레이션 S/W인 "Quartus Tool"을 기반으로 기술하고 있습니다. 해당 소프트웨어를 사용해본적 없거나 알지 못하다 하더라도 기본적인 이해를 하는데에는 전혀 지장 없습니다.!!

※1. 조합 논리의 기능

▶1. 반가산기(Half-Adder) VS 전가산기(Full-Adder)

||---------------------------------------------------------------------------------------------------------------------------------------------------------------

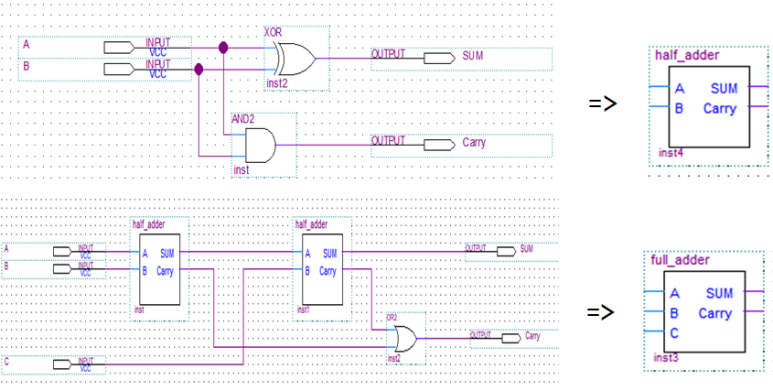

cf) Quaters tool 사용시 전가산기나 반가산기를 회로설계를 통해 하나의 심볼로 만드는 방법

ex) 반가산기 회로를 심볼로 만들고 이것을 통해 전가산기 회로를 만드는 과정

⓵ 기존의 회로설계와 동일 한 방법으로 반가산기의 회로를 설계

⓶ 설계가 완료 되면 File -> Creat/Update -> Creat Symbol File을 실행

⓷ 반가산기 회로의 저장 폴더에 .bsf파일과 .bdf파일이 존재 하는데 이것을 복사한다.

⓸ 전가산기를 구성할 때 저장할 폴더에 해당 파일들을 붙여넣기 한다.

⓹ 이후 Quaters Tool에서 반가산기를 심볼을 찾아 사용가능하고 이것으로 전가산기에 필요한 반가산기회로를 심볼로 간단하게 사용가능하다.

- ⓶에서 저장된 파일들의 이름변경이 있으면 오류가 발생할 수 있으므로 파일의 이름을 바꾸지 않도록 주의한다.

- 만들어진 심볼을 마우스 우클릭을 통해 좌우,상하 반전이 가능하여 회로에 맞게 용이하게 설정할 수 있다.

---------------------------------------------------------------------------------------------------------------------------------------------------------------||

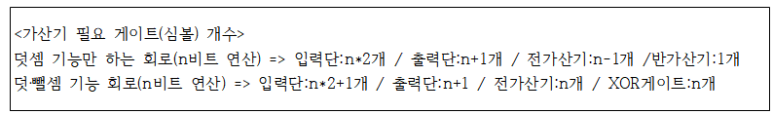

▶2. 병렬 2진 가산기

(1) 특징

- 2개의 n비트 2진수를 더하는 가산기이며, 전가산기를 연속적으로 병렬연결하여 구성하는 방법이다.

- n-비트 병렬 가산기는 n개의 전가산기를 필요로 하며, 전가산기의 출력 캐리는 다음 자리의 입력 캐리가 된다.

(2) 캐리 처리 종류 : 리플캐리(ripple carry), 룩-어헤드 캐리(Look_Ahead carry)

1. 리플캐리 : LBS에서 부터의 carry가 순차적으로 다음 전가산기로 전달되는 방식으로 전가산기의 개수(연산비트의 수가) 많을수록 많은 시간이 소요된다.

2. 룩-어헤드 캐리 : 각 전가산기 단의 출력캐리를 미리 처리하는 것으로, 입력 값에 따라 캐리 발생 혹은 캐리 전달을 미리 구하여 출력 캐리를 발생하는 것. 즉 캐리를 미리 처리해놓는 방식으로 리플캐리 방식에 비해 속도가 빠르다.

(3) 가산기의 확장

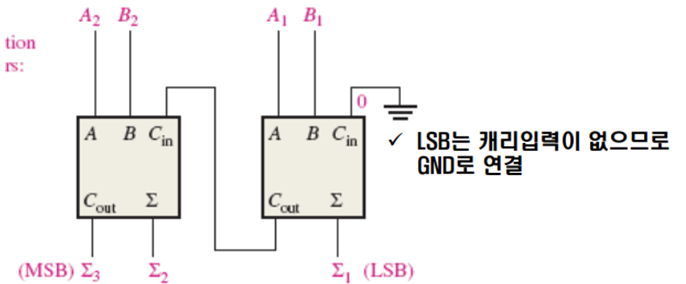

⓵ 2-비트 가산기(리플캐리 방식)

+)LSB의 는 half-adder로 하면 C_in처리가 없으므로 half-adder로 하는 것이 더 편하다.

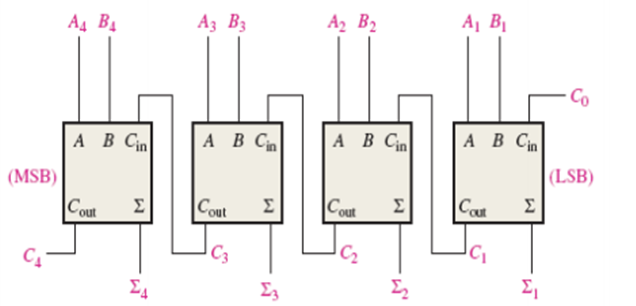

⓶ 4-비트 가산기(리플캐리 방식)

+) C_4는 모든 전가산기의 캐리가 전달된 이후 출력 되므로 앞서 언급한 데로 덧셈 연산에 시간지연을 일으킨다.

(4) 덧·뺄셈기의 설계

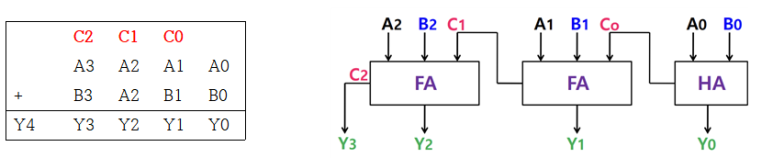

⓵ 간단한 형태 구상하기

⓶ 구성 심볼 확인(덧셈기능)

-Half-adder : 1개, Full-adder : 2개, Input: 6개, Output:4개

=> Full-adder와 Half-adder는 심볼을 만들어 사용하는 것을 권장한다.

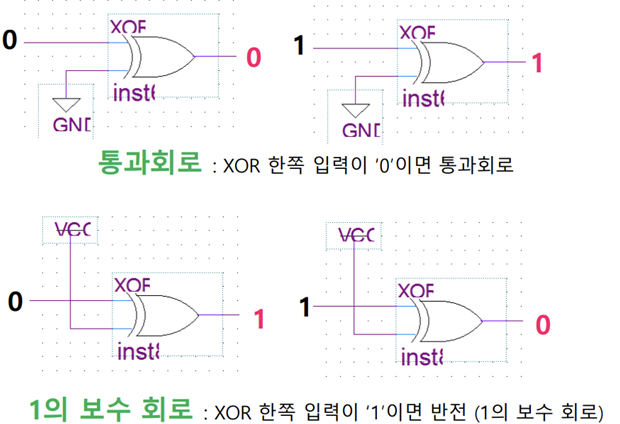

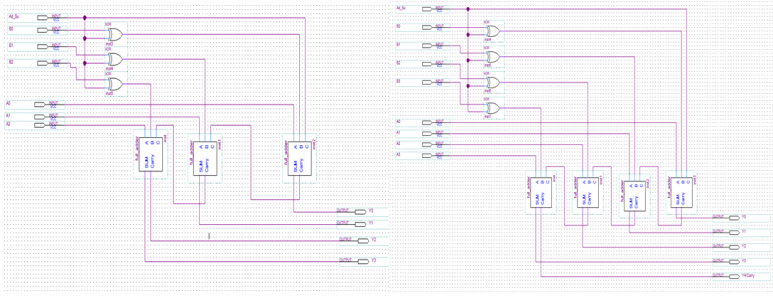

⓷ 덧·뺄셈 구분 시스템

=> XOR게이트의 특성을 이용하여 하나의 입력단에 GND(0)을 사용하고 나머지 입력단에는 원래의 입력을 사용하면 기존과 동일한 뎃셈 형태의 회로 구성이 된다.

=> 반대로 한쪽의 입력단에 VCC(1)을 사용하고 나머지 입력단에는 원래의 입력을 사용하면 1의 보수 형태(Invert)의 출력이 나오고 여기서 VCC(1)을 더하면 2의 보수 형태를 가져 부호 반전을 통해 뺄셈 연산을 할 수 있다.

⓸ Full-adder, Half-adder symbol 제작 후 bdf, bsf 해당 회로 저장 폴더에 파일 복사

⓹ 회로 설계 (좌측 3비트 덧·뺄셈 연산회로 우측: 4비트 덧·뺼셈 연산회로)

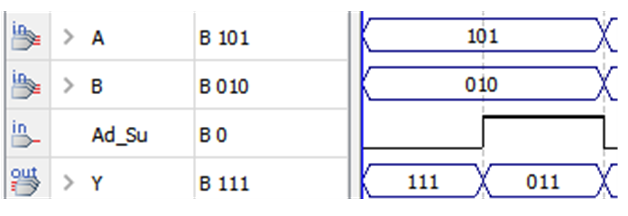

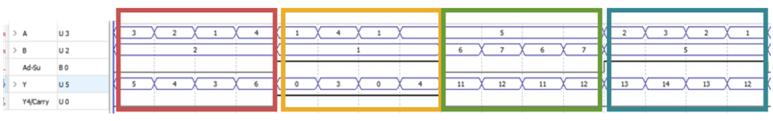

⑥ 3Bit 뺄셈기의 타이밍도 설계

ex1) 101 + 010 = 111

ex2) 101 - 010 = 011

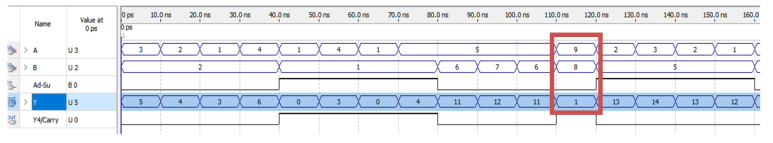

⑦ 10진수(4bit)의 덧·뺄셈기 타이밍도 설계

ex1)3214+2222 = 5436

ex2)1415-1111 = 0304

ex3)5555+6767 = 12322

ex4)2321-5555 = -3234

=> 10진수 기준에서 언더, 오버 플로우(10초과)의 경우 각 비트의 16까지 그래로 10진수로 표현된다.

||---------------------------------------------------------------------------------------------------------------------------------------------------------------

cf) 합이 16을 초과하는 경우

-다시 16이 되는 순간 0으로 돌아가 합이 17인 경우는 1로 표현된다.

---------------------------------------------------------------------------------------------------------------------------------------------------------------||

주의!)

- 타이밍도를 설계 할 때 입출력 모두 MSB를 최상위에 위치 한 BUS로 묶어야한다.

- 뺄셈시에는 MSB의 Carry비트가 포함될 경우 해당 비트가 자동으로 더해져서 원하는 결과와 다른 결과 값을 가지므로 뺄셈이 들어간 회로의 경우 MSB의 carry bit는 제외하고 그룹화한다.

'University curriculum > [Course] Digital Engineering' 카테고리의 다른 글

| [디지털 공학(15)] Data transmission (데이터 전송기) - 디코더, 인코더 _조합논리회로(3) (0) | 2024.05.10 |

|---|---|

| [디지털 공학(14)] 비교기 ( Comparator ) _ 조합논리회로(2) (0) | 2024.05.10 |

| [디지털 공학(12)] NAND와 NOR 게이트의 범용성 (0) | 2024.05.09 |

| [디지털 공학(11)] 논리회로의 해석(조합논리회로, 순서논리회로) (0) | 2024.05.09 |

| [디지털 공학(10)] 카르노맵 (0) | 2024.05.09 |

전자공학 블로그에 오신 것을 환영합니다! 최신 기술 동향, 회로 설계, 반도체 및 전자 부품에 대한 유용한 정보와 실습 팁을 제공합니다.

![[디지털 공학(15)] Data transmission (데이터 전송기) - 디코더, 인코더 _조합논리회로(3)](https://img1.daumcdn.net/thumb/R750x0/?scode=mtistory2&fname=https%3A%2F%2Fblog.kakaocdn.net%2Fdn%2F7sbLp%2FbtsHbkYcxVb%2FWHdJaxGxIjZ7ScnQeJyeb1%2Fimg.png)

![[디지털 공학(14)] 비교기 ( Comparator ) _ 조합논리회로(2)](https://img1.daumcdn.net/thumb/R750x0/?scode=mtistory2&fname=https%3A%2F%2Fblog.kakaocdn.net%2Fdn%2FbmCuQk%2FbtsHb7X3SGO%2FAILV94Lk9Q2xzPtHIrT670%2Fimg.png)

![[디지털 공학(12)] NAND와 NOR 게이트의 범용성](https://img1.daumcdn.net/thumb/R750x0/?scode=mtistory2&fname=https%3A%2F%2Fblog.kakaocdn.net%2Fdn%2FI3fqk%2FbtsHdevnEqy%2Fdo6t1Do74Su1et1bjaqS5k%2Fimg.png)

![[디지털 공학(11)] 논리회로의 해석(조합논리회로, 순서논리회로)](https://img1.daumcdn.net/thumb/R750x0/?scode=mtistory2&fname=https%3A%2F%2Fblog.kakaocdn.net%2Fdn%2Fqf5UK%2FbtsHdvYdnDm%2FUacqQSQ2Q8WbIL4X8jVms0%2Fimg.png)