![[디지털 공학(12)] NAND와 NOR 게이트의 범용성](https://img1.daumcdn.net/thumb/R750x0/?scode=mtistory2&fname=https%3A%2F%2Fblog.kakaocdn.net%2Fdn%2FI3fqk%2FbtsHdevnEqy%2Fdo6t1Do74Su1et1bjaqS5k%2Fimg.png)

안녕하세요.

이번 포스트에서는 FPGA에서 프로그래밍된 회로를 형성 시킬때 NAND와 NOR만을 사용하고 나머지 논리에 대한 회로는 사용하지 않고 NAND와 NOR로 해당 논리를 만들어 사용하게 됩니다. 어떻게 이것이 가능한지에 대하여 기술하겠습니다.

이번시간에 작성할 내용에는 지난 포스트에서 기술한 논리연산의 대치와 관련된 내용이 있습니다. 본문에 이해가 어려울시 아래 링크 읽어보세요~

https://semicircuit.tistory.com/29

[디지털 공학(11)] 논리회로의 해석(조합논리회로, 순서논리회로)

안녕하세요.이번 시간에는 조합 논리회로와 순서 논리회로를 비교하고 드모르간 또는 불 대수 연산으로부터 대치(동일하다고 표현) 가능한 논리연산에 대해 작성하겠습니다. ※1. 논리회로의

semicircuit.tistory.com

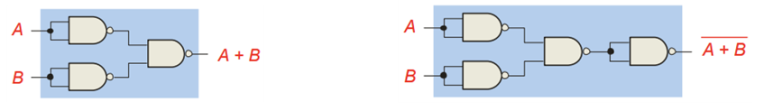

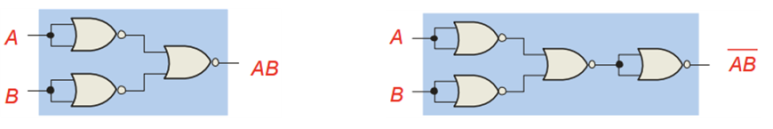

※1. NAND게이트의 범용성

▶1. Gate Symbol

- NAND게이트 한 종류 여러 가지 GATE 역할을 수행 할 수 있다.

⓵ Inverter ⓶ AND gate

⓷ OR gate ⓸ NOR gate

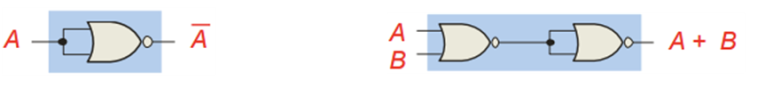

▶2. NOR게이트 범용성

- NOR게이트 한 종류 여러 가지 GATE 역할을 수행 할 수 있다.

⓵ Inverter ⓶ OR gate

⓷ AND gate ⓸ NAND gate

※2. 조합 논리회로 설계 및 간략화

- 회로 통한 진리표를 보고 논리식 설계 후

⓵불 대수(드모르간 법칙 포함) 방법과

⓶카르노맵을 이용하여 간략화를 할 수 있다.

=> 이전 포스트의 내용과 동일 하여 자세한 내용은 아래 링크를 참조해주세요.

https://semicircuit.tistory.com/29

'University curriculum > [Course] Digital Engineering' 카테고리의 다른 글

| [디지털 공학(14)] 비교기 ( Comparator ) _ 조합논리회로(2) (0) | 2024.05.10 |

|---|---|

| [디지털 공학(13)] 조합논리의 기능(반가산기, 전가산기 설계 // 덧셈기, 덧뺄셈기) _ 조합논리회로 (1) (0) | 2024.05.09 |

| [디지털 공학(11)] 논리회로의 해석(조합논리회로, 순서논리회로) (0) | 2024.05.09 |

| [디지털 공학(10)] 카르노맵 (0) | 2024.05.09 |

| [디지털 공학(9)] 부울 대수와 논리 간략화 (0) | 2024.05.09 |

전자공학 블로그에 오신 것을 환영합니다! 최신 기술 동향, 회로 설계, 반도체 및 전자 부품에 대한 유용한 정보와 실습 팁을 제공합니다.

![[디지털 공학(14)] 비교기 ( Comparator ) _ 조합논리회로(2)](https://img1.daumcdn.net/thumb/R750x0/?scode=mtistory2&fname=https%3A%2F%2Fblog.kakaocdn.net%2Fdn%2FbmCuQk%2FbtsHb7X3SGO%2FAILV94Lk9Q2xzPtHIrT670%2Fimg.png)

![[디지털 공학(13)] 조합논리의 기능(반가산기, 전가산기 설계 // 덧셈기, 덧뺄셈기) _ 조합논리회로 (1)](https://img1.daumcdn.net/thumb/R750x0/?scode=mtistory2&fname=https%3A%2F%2Fblog.kakaocdn.net%2Fdn%2FbupB76%2FbtsHed35Ljo%2F7LXgMKrS3XCp4v2kCNJRT1%2Fimg.png)

![[디지털 공학(11)] 논리회로의 해석(조합논리회로, 순서논리회로)](https://img1.daumcdn.net/thumb/R750x0/?scode=mtistory2&fname=https%3A%2F%2Fblog.kakaocdn.net%2Fdn%2Fqf5UK%2FbtsHdvYdnDm%2FUacqQSQ2Q8WbIL4X8jVms0%2Fimg.png)

![[디지털 공학(10)] 카르노맵](https://img1.daumcdn.net/thumb/R750x0/?scode=mtistory2&fname=https%3A%2F%2Fblog.kakaocdn.net%2Fdn%2FOAoIQ%2FbtsHbQvxeYU%2FHD8b1aV0WcT7lbeeH9enJk%2Fimg.png)